# High-Efficiency 3A, 24V Input Synchronous Step Down Converter

#### **Features**

- Low R<sub>DS(ON)</sub> for internal switches (top/bottom) 80mΩ/40mΩ, 3.0A

- 4.5-24V input voltage range

- High-Efficiency Synchronous-Mode

- Internal soft start limits the inrush current

- Over Current protection

- Output short circuit protection with hiccup mode

- Thermal shutdown

- Available in TSOT23-6 packages

#### **Applications**

- Portable Navigation Device

- Set Top Box

- Portable TV

- LCD TV

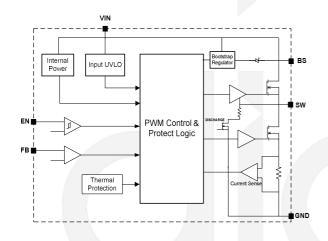

#### **Function Block**

#### **Descriptions**

The DIO69309 is high-efficiency, high frequency synchronous step-down DC-DC regulator ICs capable of delivering up to 3A output currents. The DIO69309 family operate over a wide input voltage range from 4.5V to 24V and integrate main switch and synchronous switch with very low  $R_{DS(ON)}$  to minimize the conduction loss.

The pure COT architecture with Pseudo fixed switching frequency operation provides fast transient response and eases loop stabilization. Protection features include over-current protection and thermal shutdown.

DIO69309 always operate in continuous conduction mode, which reduces the output ripple voltage in light load compared to discontinuous conduction mode. The DIO69309 is stable with extremely low ESR, high capacitance. The DIO69309 requires a minimal number of readily-available, standard, external components and is available in a space-saving TSOT23-6 package.

### **Ordering Information**

| Order Part Number | Top Marking |       | T <sub>A</sub> | Package  |                   |

|-------------------|-------------|-------|----------------|----------|-------------------|

| DIO69309TST6      | W309        | Green | -40 to 85°C    | TSOT23-6 | Tape & Reel, 3000 |

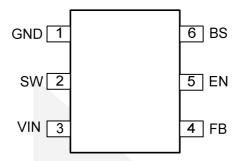

# **Pin Assignments**

TSOT23-6

Figure 1 Pin Assignment (Top View)

### **Pin Definitions**

| Pin Name | Description                                                                                                                                                                       |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND      | Power Ground                                                                                                                                                                      |

| SW       | Inductor pin. Connect this pin to the switching node of inductor.                                                                                                                 |

| VIN      | Power Input                                                                                                                                                                       |

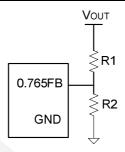

| FB       | Output Feedback Pin. Connect this pin to the center point of the output resistor divider (as shown in Figure 1) to program the output voltage: V <sub>OUT</sub> =0.765*(1+R1/R2). |

| EN       | Enable control. Pull high to turn on. Do not float.                                                                                                                               |

| BS       | Bootstrap. Connect a capacitor and a resistor between SW and BS pins to form a floating supply across the high-side switch driver. Recommend to use 0.1µF BS capacitor.           |

# **Absolute Maximum Ratings**

Stresses beyond those listed under "Absolute Maximum Rating" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maxim rating conditions for extended periods may affect device reliability.

| Parameter                  |                 | Rating               | Unit |      |

|----------------------------|-----------------|----------------------|------|------|

| Supply Voltage (V+ – V-)   |                 | 28                   | V    |      |

| EN, SW Voltage             |                 | V <sub>IN</sub> +0.3 | V    |      |

| FB Voltage                 |                 |                      | 6    | V    |

| BS Voltage                 |                 | SW+6                 | V    |      |

| Deckage Thermal Projetance | ӨЈА             |                      | 87.9 | °C/W |

| Package Thermal Resistance | Ө <sub>JC</sub> |                      | 42.2 | C/VV |

| Storage Temperature Range  |                 | -65 to 150           | °C   |      |

| Junction Temperature Range |                 | 150                  | °C   |      |

| Lead Temperature Range     |                 | 260                  | °C   |      |

# **Recommend Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended Operating conditions are specified to ensure optimal performance to the datasheet specifications. DIOO does not Recommend exceeding them or designing to Absolute Maximum Ratings.

| Parameter                  | Rating     | Unit |  |

|----------------------------|------------|------|--|

| Supply Voltage             | 4.5 to 24  | V    |  |

| Junction Temperature Range | -40 to 125 | °C   |  |

| Ambient Temperature Range  | -40 to 85  | °C   |  |

#### **Electrical Characteristics**

$V_{IN}$  = 12V,  $V_{OUT}$  = 1.2V, L = 1.5 $\mu$ H,  $C_{OUT}$  = 47 $\mu$ F, Tj = -40°C to 125°C,  $I_{OUT}$ =1A unless otherwise specified.

| Symbol                          | Parameter                                                 | Test Conditions                                              | Min            | Тур            | Max            | Unit |

|---------------------------------|-----------------------------------------------------------|--------------------------------------------------------------|----------------|----------------|----------------|------|

| V <sub>IN</sub>                 | Input Voltage Range                                       |                                                              | 4.5            |                | 24             | V    |

| IQ                              | Quiescent Current                                         | I <sub>OUT</sub> =0, V <sub>FB</sub> =V <sub>REF</sub> ·105% |                | 700            | 1000           | μA   |

| I <sub>SHDN</sub>               | Shutdown Current                                          | EN=0                                                         |                | 5              | 10             | μΑ   |

| V <sub>REF</sub>                | Feedback Reference Voltage                                | Tj = -40°C to 125°C<br>Tj = 0°C to 125°C                     | 0.745<br>0.750 | 0.765<br>0.765 | 0.780<br>0.780 | V    |

| I <sub>FB</sub>                 | FB Input Current                                          | V <sub>FB</sub> =3.3V                                        | -50            |                | 50             | nA   |

| R <sub>DS(ON)</sub>             | Top FET R <sub>ON</sub>                                   | T <sub>A</sub> = 25°C                                        |                | 80             |                | mΩ   |

| R <sub>DS(ON)</sub>             | Bottom FET R <sub>ON</sub>                                | T <sub>A</sub> = 25°C                                        |                | 40             |                | mΩ   |

| I <sub>LIM</sub> <sup>(1)</sup> | Low side power FET current limit                          |                                                              | 3.3            | 3.9            | 4.5            | А    |

| V <sub>ENH</sub>                | EN Rising Threshold                                       |                                                              | 1.5            |                |                | ٧    |

| V <sub>ENL</sub>                | EN Falling Threshold                                      |                                                              |                |                | 0.4            | ٧    |

| V <sub>UVLO</sub>               | V <sub>IN</sub> Under-Voltage Unlock<br>Threshold, Rising |                                                              | 3.65           | 4.05           | 4.45           | V    |

|                                 | Hysteresis V <sub>IN</sub> voltage                        |                                                              | 0.3            | 0.4            | 0.5            | V    |

| f <sub>SW</sub>                 | Switching Frequency                                       |                                                              | 600            | 700            | 800            | kHz  |

|                                 | Min ON Time                                               |                                                              |                | 140            |                | ns   |

|                                 | Min OFF Time                                              |                                                              |                | 90             | 140            | ns   |

|                                 | Maximum Duty Cycle                                        |                                                              |                | 90%            |                |      |

| T <sub>SS</sub>                 | Soft Start Time                                           |                                                              |                | 1              |                | ms   |

| T <sub>SD</sub>                 | Thermal Shutdown Temperature                              |                                                              |                | 148            |                | °C   |

| T <sub>HYS</sub>                | Thermal Shutdown Hysteresis                               |                                                              |                | 20             |                | °C   |

<sup>(1)</sup> Not production tested.

Specifications subject to change without notice.

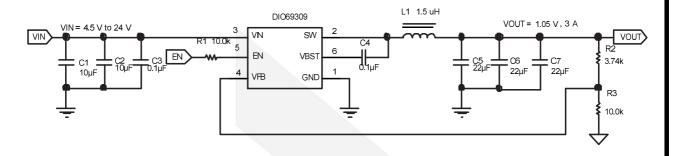

# **Typical Application**

DIO69309 4.5V to 24V Input, 1.05V Output Converter

Figure. DIO69309 1.05V/3A Reference Design

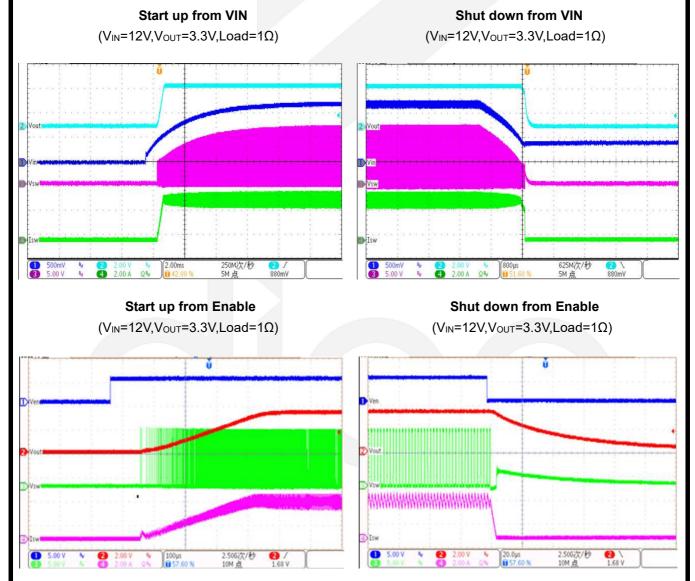

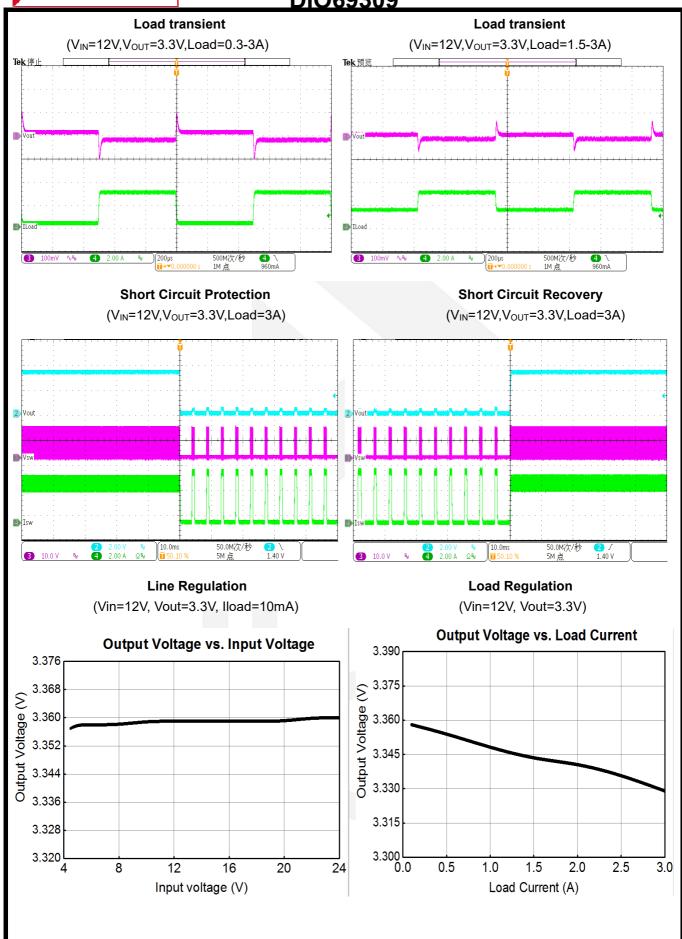

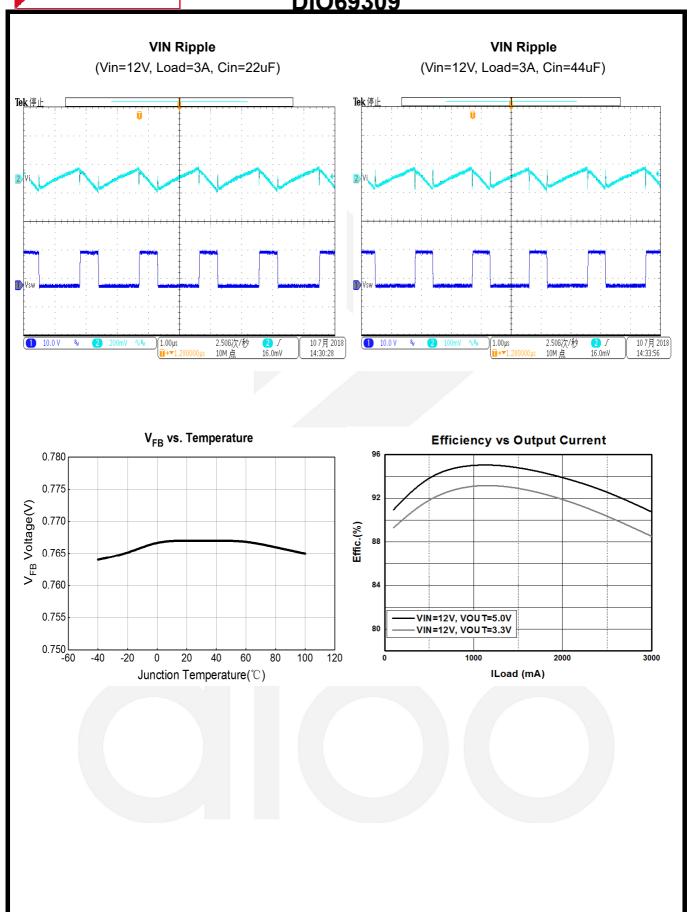

# **Typical Performance Characteristics**

### **Application Information**

DIO69309 is a synchronous buck regulator IC that integrates the pure COT control, top and bottom switches on the same die to minimize the switching transition loss and conduction loss. With ultra low R<sub>DS(ON)</sub> power switches and proprietary pure COT control, this regulator IC can achieve the highest efficiency and the highest switch frequency simultaneously to minimize the external inductor and capacitor size, and thus achieving the minimum solution footprint.

**Table 1. Design Parameters**

| PARAMETER             | VALUE         |  |  |

|-----------------------|---------------|--|--|

| Input voltage range   | 4.5 V to 24 V |  |  |

| Output voltage        | 1.05 V        |  |  |

| Output current        | 3 A           |  |  |

| Output voltage ripple | 20 mVpp       |  |  |

**Table 2. Recommended Component Values**

| OUTPUT      | R2   | R3 (kΩ) | L1 (µH) |     |     | 05 + 00 (5)  |

|-------------|------|---------|---------|-----|-----|--------------|

| VOLTAGE (V) | (kΩ) |         | MIN     | TYP | MAX | C5 + C6 (μF) |

| 1           | 3.09 | 10.0    | 1       | 1.5 | 2.2 | 44 - 66      |

| 1.05        | 3.74 | 10.0    | 1       | 1.5 | 2.2 | 44 - 66      |

| 1.2         | 5.76 | 10.0    | 1       | 1.5 | 2.2 | 44 - 66      |

| 1.5         | 9.53 | 10.0    | 1       | 1.5 | 2.2 | 44 - 66      |

| 1.8         | 13.7 | 10.0    | 1       | 1.5 | 2.2 | 44 - 66      |

| 2.5         | 22.6 | 10.0    | 1.5     | 2.2 | 3.3 | 44 - 66      |

| 3.3         | 33.2 | 10.0    | 1.5     | 2.2 | 3.3 | 44 - 66      |

| 5           | 54.9 | 10.0    | 1.5     | 3.3 | 4.7 | 44 - 66      |

Because of the high integration in the DIO69309 IC, the application circuit based on this regulator IC is rather simple. Only input capacitor  $C_{\text{IN}}$ , output capacitor  $C_{\text{OUT}}$ , output inductor L and feedback resistors (R1 and R2) need to be selected for the targeted applications specifications.

#### Feedback resistor dividers R1 and R2

Choose R1 and R2 to program the proper output voltage. To minimize the power consumption under light loads, it is desirable to choose large resistance values for both R1 and R2. A value of between 10k and 1M is highly recommended for both resistors. If Vout is 3.3V, R1=40.2k is chosen, then R2 can be calculated to be 12k.

$$R_2 = \frac{0.765V}{V_{OUT} - 0.765V} R_1$$

#### **Current Protection**

The output over-current limit (OCL) is implemented using a cycle-by-cycle valley detect control circuit. The switch current is monitored during the OFF state by measuring the low-side FET drain to source voltage. This voltage is proportional to the switch current. To improve accuracy, the voltage sensing is temperature compensated. During the on time of the high-side FET switch, the switch current increases at a linear rate determined by Vin, Vout, the on-time and the output inductor value.

During the on time of the low-side FET switch, this current decreases linearly. The average value of the switch current is the load current lout. If the monitored current is above the OCL level, the converter maintains low-side FET on and delays the creation of a new set pulse, even the voltage feedback loop requires one, until the current level becomes OCL level or lower. In subsequent switching cycles, the on-time is set to a fixed value and the current is monitored in the same manner. If the over current condition exists consecutive switching cycles, the internal OCL threshold is set to a lower level, reducing the available output current. When a switching cycle occurs where the switch current is not above the lower OCL threshold, the counter is reset and the OCL threshold is returned to the higher value.

There are some important considerations for this type of over-current protection. The load current is higher than the over-current threshold by one half of the peak-to-peak inductor ripple current. Also, when the current is being limited, the output voltage tends to fall as the demanded load current may be higher than the current available from the converter. This may cause the output voltage to fall. When the VFB voltage falls below the UVP threshold voltage, the UVP comparator detects it. And then, the device will shut down after the UVP delay time (typically 14µs) and re-start after the hiccup time (typically 8ms).

When the over current condition is removed, the output voltage returns to the regulated value.

#### **UVLO Protection**

Under voltage lock out protection (UVLO) monitors the device input voltage. When the voltage is lower than UVLO threshold voltage, the device is shut off. This protection is non-latching.

#### **Thermal Shutdown**

The device monitors the temperature of itself. If the temperature exceeds the threshold value (typically 155°C), the device is shut off. This is a non-latch protection.

#### Input capacitor CIN

This ripple current through input capacitor is calculated as:

$$I_{CIN\_RMS} = I_{OUT} \cdot \sqrt{D(1-D)}$$

This formula has a maximum at V<sub>IN</sub>=2V<sub>OUT</sub> condition, where I<sub>CIN\_RMS</sub>=I<sub>OUT</sub>/2. This simple worst-case condition is commonly used for DC/DC design.

To minimize the potential noise problem, place a typical X5R or better grade ceramic capacitor really close to the IN and GND pins. Care should be taken to minimize the loop area formed by C<sub>IN</sub>, and IN/GND pins. In this case, a 10µF low ESR ceramic capacitor is recommended.

#### **Output capacitor Cout**

The output capacitor is selected to handle the output ripple noise requirements. Both steady state ripple and transient requirements must be taken into consideration when selecting this capacitor. For the best performance, it is recommended to use X5R or better grade ceramic capacitor greater than 22µF capacitance.

#### **Output inductor L:**

There are several considerations in choosing this inductor.

1) Choose the inductance to provide the desired ripple current. It is suggested to choose the ripple current to be about 40% of the maximum output current. The inductance is calculated as:

$$L = \frac{Vout(1 - Vout / V_{IN, MAX})}{F_{SW} \times I_{OUT, MAX} \times 40\%}$$

where Fsw is the switching frequency and I<sub>OUT,MAX</sub> is the maximum load current. The DIO69309 regulator IC is quite tolerant of different ripple current amplitude. Consequently, the final choice of inductance can be slightly off the calculation value without significantly impacting the performance.

The saturation current rating of the inductor must be selected to be greater than the peak inductor current under full load conditions.

$$I_{SAT,MIN} > I_{OUT,MAX} + \frac{V_{OUT}(1 - V_{OUT}/V_{IN,MAX})}{2 \cdot F_{SW} \cdot L}$$

3) The DCR of the inductor and the core loss at the switching frequency must be low enough to achieve the desired efficiency requirement. It is desirable to choose an inductor with DCR<50mΩ to achieve a good overall efficiency.

#### **Layout Design:**

The layout design of DIO69309 regulator is relatively simple. For the best efficiency and minimum noise problems, we should place the following components close to the IC: C<sub>IN</sub>, L, R1 and R2.

- 1) It is desirable to maximize the PCB copper area connecting to GND pin to achieve the best thermal and noise performance. If the board space allowed, a ground plane is highly desirable.

- 2) C<sub>IN</sub> must be close to Pins IN and GND. The loop area formed by C<sub>IN</sub> and GND must be minimized.

- 3) The PCB copper area associated with SW pin must be minimized to avoid the potential noise problem.

- 4) The components R1 and R2, and the trace connecting to the FB pin must NOT be adjacent to the SW net on the PCB layout to avoid the noise problem.

- 5) If the system chip interfacing with the EN pin has a high impedance state at shutdown mode and the IN pin is connected directly to a power source such as a Li-lon battery, it is desirable to add a pull down  $1M\Omega$  resistor between the EN and GND pins to prevent the noise from falsely turning on the regulator at shutdown mode.

#### **CONTACT US**

**D**ioo is a professional design and sales corporation for high-quality and performance analog semiconductors. The company focuses on industry markets, such as, cell phone, handheld products, laptop, and medical equipment and so on. Dioo's product families include analog signal processing and amplifying, LED drivers and charger IC. Go to <a href="http://www.dioo.com">http://www.dioo.com</a> for a complete list of Dioo product families.

For additional product information, or full datasheet, please contact with our Sales Department or Representatives.